厂商 :北京华清方辰科技发展有限公司

北京市 北京市- 主营产品:

- 实验系统

- 教学仪器

- 单片机接口

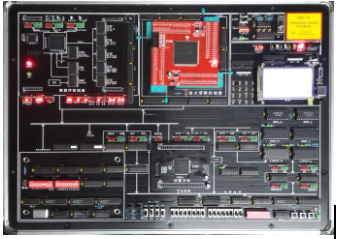

HQFC-B5计算机组成原理综合实验系统(华清方辰)

HQFC-B5是16位机教学系统。适用于本科、硕士研究生的计算机组成原理和计算机系统结构课程的教学实验。该系统有自己的指令系统和监控程序,能够与终端或PC机相连(可以通过键盘输入程序执行,结果可以通过指示灯或者显示器显示),可以进行联机操作和执行比较完整的程序。实验系统分成主要的两个部分:一部分采用模块化的结构(运算器、控制器、主存储器、I/O接口和中断)构成一台完整的模型计算机,支持组合逻辑控制器和微程序控制器两种控制器方案,两种控制器紧凑合理,完成教学实验方便高效;另一部分采用先进的FPGA芯片(采用ALTERA公司的EP1C12Q240芯片),用户可自行设计CPU(可以含流水和CACHE)。系统的软硬件配置完整,技术资料齐全,支持的实验项目多、水平高,实验手段先进。

一、主要技术指标

1、机器字长16位,即运算器、主存、数据总线、地址总线均是16位。

2、指令系统支持多种基本寻址方式。其中部分指令已实现,用于设计监控程序和用户的常规汇编程序,尚保留多条指令供用户自己实现。

3、主存最大寻址空间是18K字,基本容量为8K字节(或16位字)的E2PROM和2K字节(或16位字)的RAM存储区域。可进行主存储器扩展实验。当扩展存储器当主存储器使用时,可用做用户的监控系统,而不破坏原监控系统,非常方便教学。

4、运算器由一片CPLD构成,采用ALTERA公司的EPM1270芯片,ALU实现8种算术与逻辑运算功能, 内部包括16个双端口读出、单端口写入的通用寄存器, 和一个能自行移位的乘商寄存器。设置C、Z、 V、S四个状态标志位。用户也可自行自己的运算器,采用USB下载,使用非常方便。

5、控制器采用微程序和硬布线两种控制方案实现, 用户可根据自己的需要选择。微程序控制器采用计算机COM口在线进行更改,非常方便用户自行设计自已的微程序控制器。硬布线控制器采用一片FPGA(30万逻辑门),使用USB下载,可完成用户自行设计的多种控制器。

6、主机上安装有一路INTEL8251串行接口,可直接接计算机终端, 或接入一台PC机作为自己的仿真终端。选用了MAX202倍压线路,以避免使用+12V和-12V电源。另保留一路为用户扩展用。用户可完成串口初始化,双机通讯等实验。

7、主机可完成三级中断实验和中断嵌套实验。

8、在主板上设有扩展实验接口和扩展实验区,提供扩展内存和各种/输出接口实验所需的地址、数据和控制等信号,以便支持在主板上完成这类扩展实验。

9、提供多种扩展接口实验小板(用户选购)。

10、实验箱由已实现指令构成的的监控程序(操作系统),可以完成常用的DEBUG命令:A命令、D命令、U命令、G命令等。 支持多种实验方式(如:单步/连续,手动置指令/从内存读指令等),监控源码开放,用户可以修改或使用自己的监控程序。

11、实验箱上的FPGA芯片也可用于实现各种时序电路和组合逻辑电路实验,采用 ALTERA公司的EP1C12Q240芯片,采用USB下载方式,方便用户使用。

12、实验箱上的FPGA芯片可以实现流水和非流水两种CPU方案,还可完成高速缓冲存储器(cache)的教学实验。

13、提供最齐全的设计、实现、操作使用的资料。包括逻辑图、可编程器件的逻辑内容, 指令格式与功能,微指令格式及微程序清单,组合逻辑的指令执行流程表及化简后的全部逻辑表达式, 监控程序的源码等内容,还包括对上述内容必要的文字说明,还可以提供PC机仿真终端程序、交叉汇编程序源程序清单。

14、提供配套的教师用书,把一些在讲课中应强调的内容,各基本实验项目的参考答案等汇集在一起,给出各基本实验的详细的操作步骤,以减轻讲课与辅导实验教师的备课负担。

15、提供上端教学软件,可方便用户编写和下载用户的微程序控制器,而且上端软件提供仿终端,方便用户教学实验,不需另外的终端显示输入设备。

16、运算器和微程序控制器、硬布线控制器、监控系统都可以由用户实验现自己的,全部采用USB口下载同,非常方便用户使用。提高学生的实验水平和实验兴趣。出厂提供参考程序,方便老师还原到出厂状态。

17、实验台提供了扩展IO实验插座和电源插座,选购不同的扩展实验板可以完成不同的实验。

二、实验内容

HQFC-B5支持的实验分为基本实验和可选实验,基本实验指学习计算机组成原理课通常要完成的实验项目, 通过这些实验可达到学习基本原理和训练基本技能的目的。可选实验是指教学机支持的那些难度较大需要较长时间完成的实验项目,这些实验可作为课程设计的内容或用作毕业设计的题目。

(一)组成原理基本实验

1、三-八译码器实验

2、hamming编码实验

3、BCD加法实验

4、移位器实验

5、加法器实验

6、乘法器实验

7、除法器实验

8、算术逻辑运算实验

9、节拍序列发生器实验

10、FIFO存储器部件实验

(二)组成原理系统基本实验

1、基础汇编语言程序设计

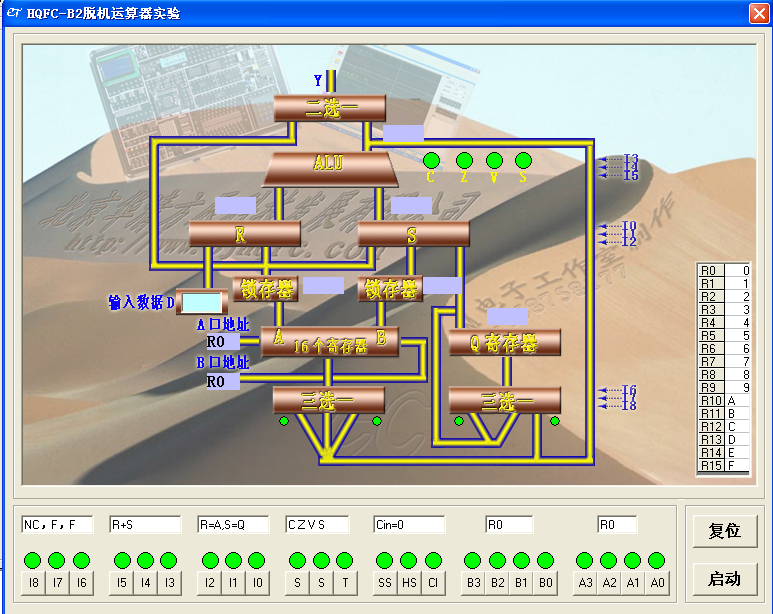

2、脱机运算器实验

3、指令测试实验

4、监控程序(BIOS程序)DEBUG常用命令测试实验

5、主存储器实验

6、可编程串行通讯口输入输出实验

7、三级中断实验

8、微程序控制器实验

9、BASIC高级语言及浮点运算实验

9、组合逻辑控制器实验

(三)、CPU设计实验

1、FPGA完成组合逻辑控制器、运算器、存储器控制、IO控制部件

2、汇编语言程序设计

3、总线IO实验

(四) 可选实验(课程设计、毕业设计用户自行完成)

1、故障诊断的设计与实现

2、用一台正确运行的实验机辅助调试另一台实验机

3、实验机的监控程序、交叉汇编程序的修改与扩充的实验

4、扩充的输入/输出接口实验

5、设计与实现一套全新指令系统的CPU

6、用FPGA(采用ALTERA公司的EP1C12Q240芯片)实现的不支持流水的CPU。

7、用FPGA(采用ALTERA公司的EP1C12Q240芯片)实现的支持流水的CPU。

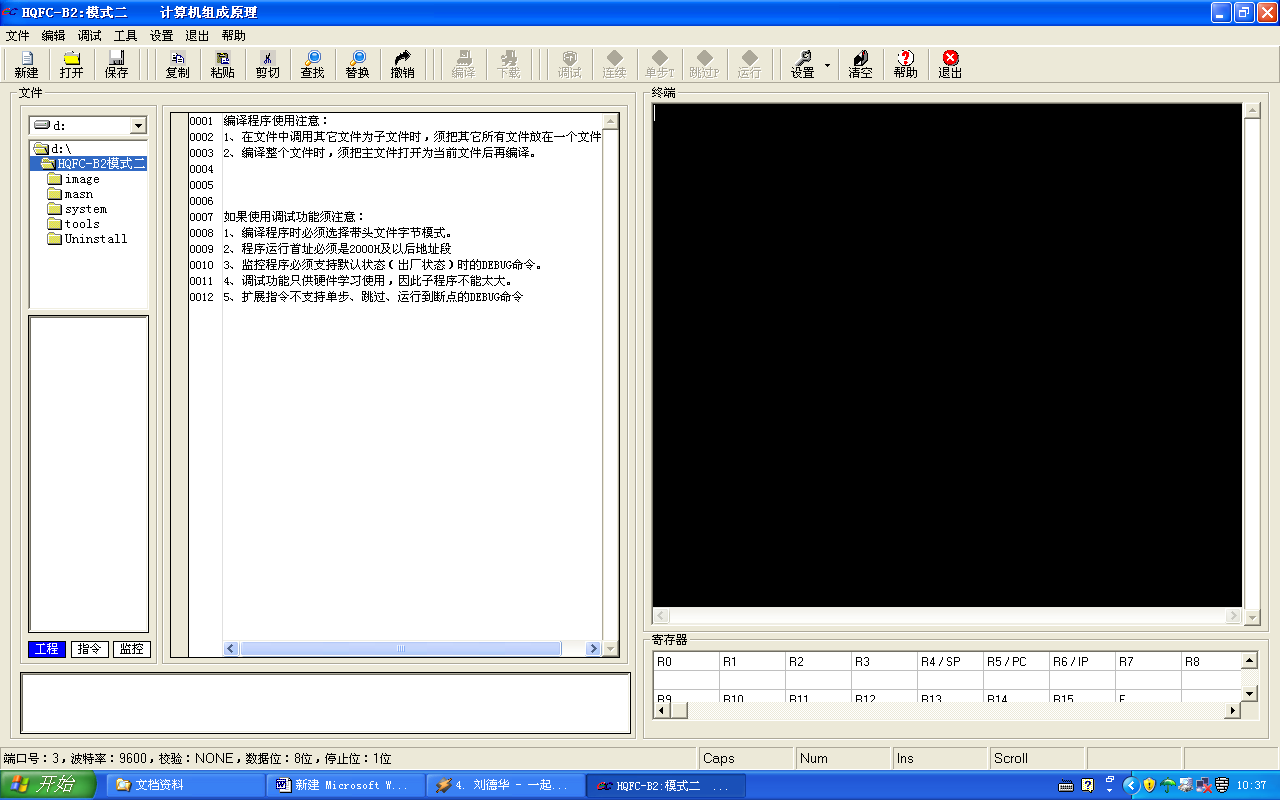

三、上端软件

1、 可以编译用户源程序,根据编译选择条件,可以支持基本指令、扩展指令、用户自定义指令(须在规则文件中指明自定义指令的规则)。

2、 可以做为实验台的仿终端显示/输入。

3、 经过通讯口下载用户的微程序控制器或恢复出厂的微程序控制器。

4、 打开/编辑微程序控制器代码。

5、 模拟脱机运算器功能。

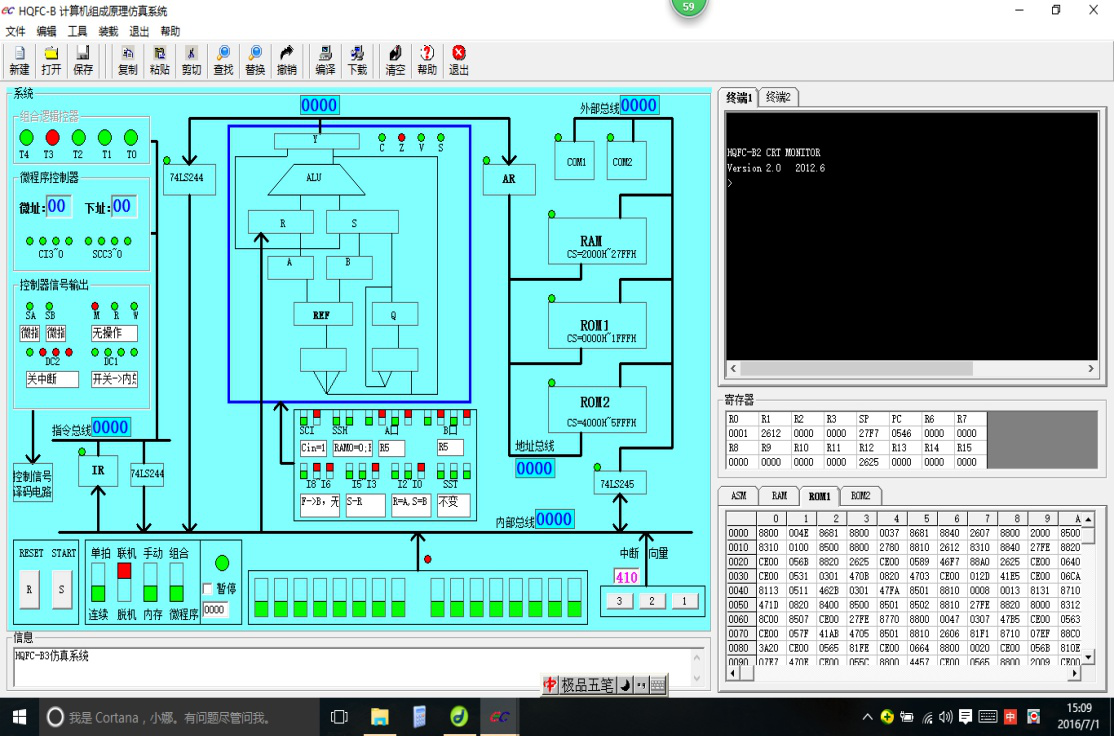

HQFC-B5教学实验软件

虚拟运算器窗口

三、多种扩展接口实验小板(选购):

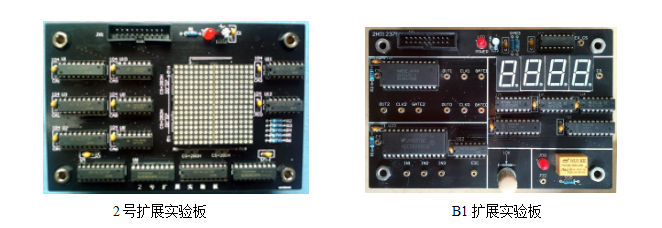

(1)、2号扩展实验板(16X16点阵(8位))

8位数据总线的16X16点阵实验。

(2)、B1扩展实验板

1、扩展8254定时器/计数器实验

2、AD0809模数转换实验

3、4位七段LED数码管显示实验

4、继电器控制实验

(3)、B2扩展实验板

1、RAM存储器扩展实验

2、8255扩展实验

四、计算机组成原理仿真软件(选购)

软件名称:HQFC-B仿真系统

详细资料查看HQFC-B仿真系统资料介绍。