厂商 :北京华清方辰科技发展有限公司

北京市 北京市- 主营产品:

- 实验系统

- 教学仪器

- 单片机接口

HQFC-B2计算机组成原理及系统结构

实验系统

北京华清方辰科技发展有限公司

计算机组成原理和计算机系统结构都是大学计算机系的重要课程。HQFC-B2适用于本科、硕士研究生的计算机组成原理和计算机系统结构课程的教学实验。支技两种模式的计算机组成原理和计算机系统结构的实验

模式一中HQFC-B实验箱的最大优点是开放式CPU设计和测试,能完成计算机组成原理和系统结构的实验,同时也可用于学生的课程设计和毕业设计。是培养学生的创新精神和实践能力、提高大学计算机教学质量的实验设备。

模式二中该系统有自己的指令系统和监控程序,能够与终端或PC机相连(可以通过键盘输入程序执行,结果可以通过指示灯或者显示器显示),可以进行联机操作和执行比较完整的程序。用户可自行设计CPU(可以含流水和CACHE)。系统的软硬件配置完整,技术资料齐全,支持的实验项目多、水平高,实验手段先进。

模式一、开放式CPU实验

(使用教材:汤志忠--开放式实验CPU设计)

一、主要技术指标

1、实验系统主要由PC监控系统,外部程序存储器,FPGA及其相关下载电路,以及控制电路组成。

2、16位CPU基本指令系统支持多种寻址方式。用户可按照需要自行设计CPU指令系统,从而实现指令系统和CPU系统结构的可变性。

3、上端软件能够按一个时钟脉冲、半个时钟和连续运行三种方式调试CPU测试程序,能够监测CPU内部的所有信号和数据。

4、外部存储器由两片HM6116器件并联构成2K X 16位的存储器。

5、FPGA(CPU)采用Altera公司cyclone系列的EP1C12Q240(出厂默认)或其它FPGA芯片。

6、三种调试模式:FPGA-CPU独立调试模式、FPGA-CPU附加外部RAM运行模式和单片机控制FPGA-CPU调试运行模式。

7、机器字长16位, 即数据总线、地址总线均是16位。

二、计算机组成原理实验

1、编码实验:Hamming码,CRC码,BCD码的加法。

2、运算器部件实验:移位器,加法器,乘法器,除法器。

3、时序部件

4、 实验CPU:通用寄存器组部件,算术逻辑部件,指令译码器,存储器部件,CPU调试,微程序控制器。

5、 EP1C612Q240内部存储器(RAM、ROM和FIFO)实验

三、计算机系统结构基本实验

1、CPU设计和调试:无流水无cache,多级流水,多级流水和cache,具有cache的超标量CPU

四、数字电路实验

1、138地址译码实验

2、8位七段LED数码管BCD码显示实验

3、16位LED发光管显示实验

4、简易计数器实验

5、简易频率计实验

6、PS键盘显示实验

7、VGA显示实验

五、上端软件

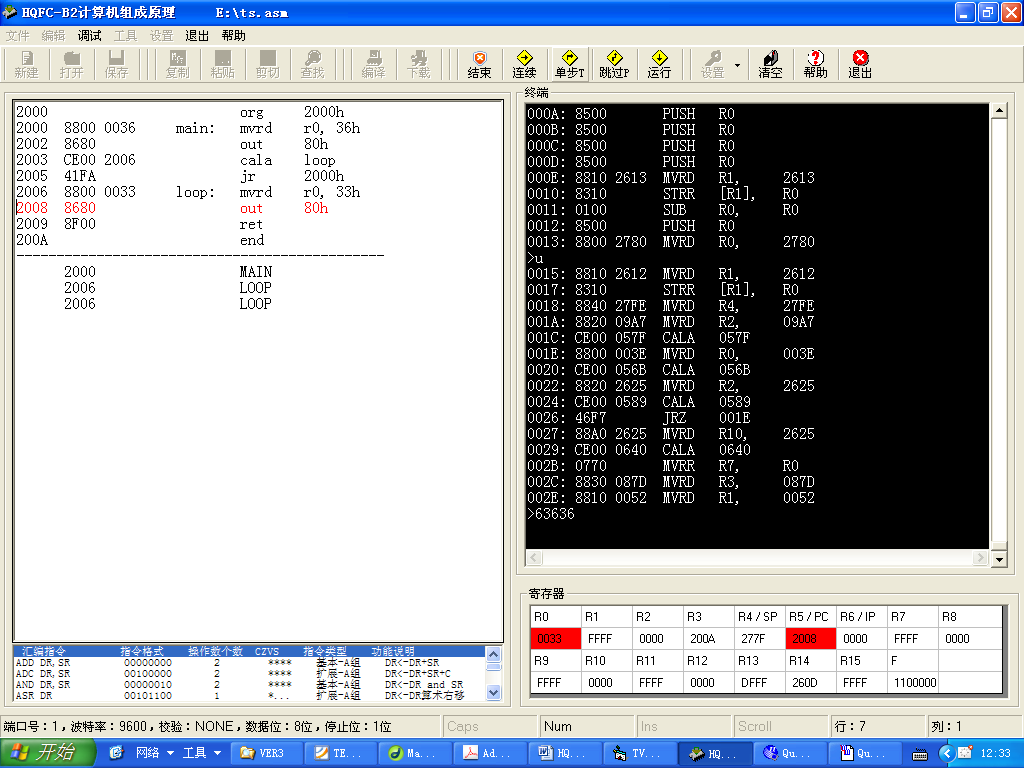

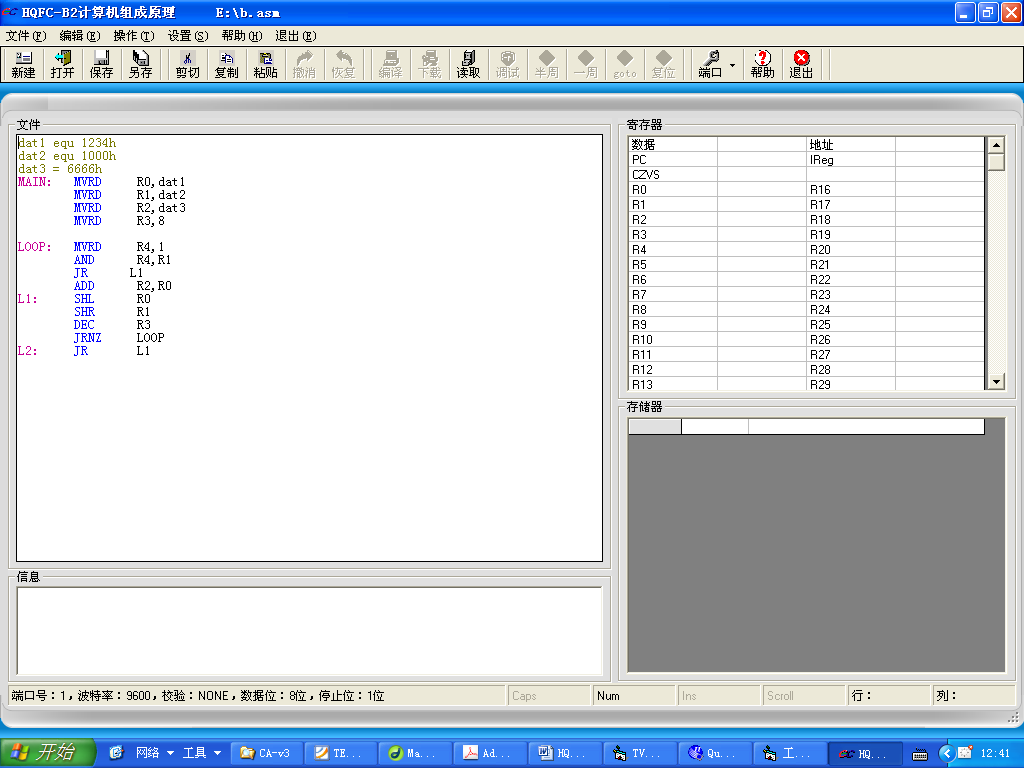

左半部为源程序或调试窗口(简单程序),右半部份为寄存器值和存储器内容显示区域。

模式二、计算机组成原理及体系结构

(使用教材:王诚--计算机组成原理)

一、主要技术指标

1、机器字长 16位(也可设计成 8 位字长的另外一个新的系统),即运算器、主存、数据总线、地址总线、指令等都是 16位。

2、完整的指令系统被划分为基本指令和扩展指令两部分,支持多种基本寻址方式。其中的基本指令已经实现,用于设计监控程序和用户的常规汇编程序,保留的多条扩展指令供实验者自己实现。

3、主存最大寻址空间是 18K 字(16 位),基本容量为 8K 字的 ROM 和 2K 字的 RAM 存储区域。另外的 8K字用于完成存储器容量扩展的教学实验。FPGA 芯片和存储器芯片之间可以通过分开的地址总线和分开的数据总线实现连接,这在实现分开的指令存储器和数据存储器的方案中是必要的。

4、运算器是参照 Am2901 芯片的组成和功能来设计的,ALU 实现 8 种算术与逻辑运算功能,

内部包括 16 个双端口读出、单端口写入的通用寄存器,和一个能自行移位的乘商寄存器。设置 C (进位)、Z(结果为 0)、V(溢出)和 S(符号位)四个状态标志位。

5、控制器采用硬连线控制器方案实现,也可修改成微程序控制器。实验人员可方便地修改已有设计。

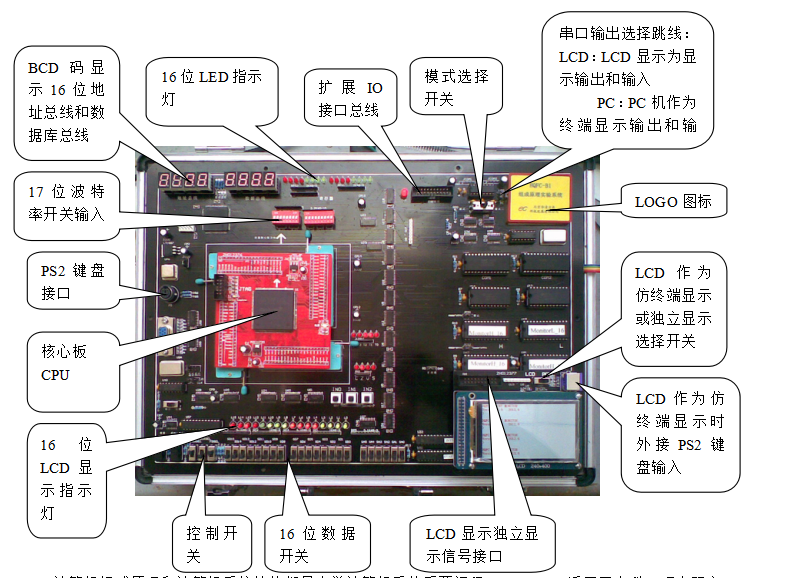

6、主机上安装有二路 INTEL8251 串行接口,可直接接计算机终端,或接入一台 PC 机作为自己的仿真终端。选用了 MAX202 倍压线路,以避免使用+12V 和-12V电源。也可以使用LCD显示板作为仿真终端。

7、两路的串行接口的接插座安放在机箱后侧板以方便接线插拔和机箱盖的打开关闭。

8、在主板上设置有一些拨数的开关和微型开关、按键和指示灯,支持最低层的手工操作方式的输入/输出和机器调试。

9、板上安装了很多发光二极管指示灯和数码管,用于显示重要的数据或控制信号的状态。

10、实验台上LCD显示屏可以进行仿终端显示或进行独立的LCD显示实验。

1)、实验台两跳线(实验台右上角)同时选择PC一端时,串口选择为PC机的COM口,同时选择LCD一端时,实验IO输出选择为液晶仿终端(LCD显示板上的开关必须选择到PCEC一端)。

2)、LCD显示板上的选择开关选择LCD一端时,LCD通过20芯扁平线和8芯扁平线与实验平台相连,由CPU直接控制LCD显示。

二、基本实验

1、编码实验:Hamming码,CRC码,BCD码的加法。

2、运算器部件实验:

1)、移位器,加法器,除法器等。

2)、模拟2901运算器基本运算功能实验。

3、时序部件

4、 EP1C12Q240内部存储器(RAM、ROM和FIFO)实验

5、基础汇编语言程序设计

6、组合逻辑控制器(硬布线控制器)实验

7、主存储器实验

8、串行口输入输出实验

9、LCD显示实验

三、可完成实验(课程设计、毕业设计(用户设计))

1、完成全部指令。

2、用FPGA实现的不支持流水的CPU(模型机)。

3、用FPGA实现的支持流水的CPU(模型机)。

4、CACHE实验。

5、FPGA实现各种组合逻辑电路和时序电路实验。

6、其它综合EDA实验。

四、数字电路/EDA实验

1、138地址译码实验

2、8位七段LED数码管BCD码显示实验

3、16位LED发光管显示实验

4、简易计数器实验

5、简易频率计实验

6、PS键盘显示实验

7、VGA显示实验

五、扩展接口实验

1、1号扩展实验板

1)8254/3定时器计数器实验

2)AD0809模数转换实验

3)4位LED数码管显示实验

4)继电器控制实验

2、5号扩展实验板

16X16LED点阵显示实验

3、15号扩展实验板

无线遥控实验

4、6号扩展实验板

红外遥控实验

5、17号扩展实验板

步进电机控制及测速实验

6、18号扩展实验板

8279键盘显示控制实验

7、19号扩展实验板

1)基本逻辑门逻辑实验

2)TTL、HC和HCT器件的电压传输特性实验

六、上端软件